?Mathematical formulae have been encoded as MathML and are displayed in this HTML version using MathJax in order to improve their display. Uncheck the box to turn MathJax off. This feature requires Javascript. Click on a formula to zoom.

?Mathematical formulae have been encoded as MathML and are displayed in this HTML version using MathJax in order to improve their display. Uncheck the box to turn MathJax off. This feature requires Javascript. Click on a formula to zoom.Abstract

Single-electron transistors (SETs) are sub-10-nm scale electronic devices based on conductive Coulomb islands sandwiched between double-barrier tunneling barriers. Chemically assembled SETs with alkanethiol-protected Au nanoparticles show highly stable Coulomb diamonds and two-input logic operations. The combination of bottom-up and top-down processes used to form the passivation layer is vital for realizing multi-gate chemically assembled SET circuits, as this combination enables us to connect conventional complementary metal oxide semiconductor (CMOS) technologies via planar processes. Here, three-input gate exclusive-OR (XOR) logic operations are demonstrated in passivated chemically assembled SETs. The passivation layer is a hybrid bilayer of self-assembled monolayers (SAMs) and pulsed laser deposited (PLD) aluminum oxide (AlO), and top-gate electrodes were prepared on the hybrid passivation layers. Top and two-side-gated SETs showed clear Coulomb oscillation and diamonds for each of the three available gates, and three-input gate XOR logic operation was clearly demonstrated. These results show the potential of chemically assembled SETs to work as logic devices with multi-gate inputs using organic and inorganic hybrid passivation layers.

1. Introduction

Novel sub-10-nm scale transistors are required for the realization of next-generation electronics, since a widely accepted design rule for semiconductor devices is that they must shrink over time, down to 5 nm within the next 10 years based on current projections [Citation1]. Nowadays, silicon-based multi-gate field effect transistors (FETs) such as Fin-FET are used in practical applications, but FETs must overcome their short-channel effects and reduce their leakage currents in order to minimize the power consumption of their electronic circuits [Citation1]. Fabrication and functionalization of novel sub-10-nm scale electronic devices based on new materials are key issues for development in the next 10 years.

Single-electron electronics have received increasing attention in recent years, because this field may lead to a new generation of faster processors with low power consumption [Citation2,Citation3]. Single-electron transistors (SETs), one candidate in the realm of sub-10-nm scale devices, are operated by Coulomb blockade effects with conductive Coulomb islands. As such, the total numberof SETs required for logic operations can be decreased by utilizing the multi-gate structure, in which the linear combination of gate voltages operates the phase shift of the Coulomb oscillation [Citation2,Citation3]. Logic operations based on single electronics with various materials such as GaAs and CdS nanowires have been reported [Citation4–Citation8].

Despite numerous efforts to reduce the size of FETs, several transistors are usually required to realize certain logic functions [Citation3]. However, combining several SETs allows for logic operation with low-energy circuits [Citation9–Citation19]. Logic operations with single carbon nanotube SETs have also been demonstrated previously [Citation20]. In both of these cases, two-gate inputs were used to demonstrate these logic properties.

Recently, we have reported chemically assembled SETs formed using top-down and bottom-up technologies. Au nanogap electrodes with double side-gate electrodes were simultaneously fabricated using electron-beam lithography (EBL) and electroless gold plating (ELGP) [Citation21–Citation25]. The narrowing of the gap separation between the electrodes is made possible by electroless Au plating and stops at 3.0 nm, owing to a self-termination mechanism [Citation26–Citation28]. The surfaces of the self-terminated nanogap electrodes are covered by alkanethiol and alkanedithiol mixed self-assembled monolayers (SAMs). Double-gate SETs were fabricated by anchoring of chemically synthesized colloidal Au nanoparticles using alkanedithiol [Citation22,Citation29,Citation30]. The fabricated SETs show highly stable and reproducible Coulomb diamonds under applied voltages at the source and gate electrodes [Citation31]. The sole SET also exhibited all usual types of two-input logic operations (XOR, XNOR, NAND, OR, NOR, and AND) with an on/off ratio of 10, indicating the potential of chemical assembly to yield highly stable SETs exhibiting all logic operations [Citation31].

Hybrid insulators of SAMs and inorganic bilayers show good gate insulator properties when used in organic thin-film transistors [Citation32–Citation35]. We have also demonstrated chemically assembled transistors made by utilizing a hybrid passivation bilayer [Citation36]. SiN was prepared by catalytic chemical vapor deposition (CAT-CVD) at 338 K onto alkanethiol and alkanedithiol mixed SAMs to form a hybrid passivation bilayer, and a top-gate electrode was added on the Au nanoparticle via an EBL overlay method at a process temperature of 423 K [Citation36,Citation37]. Even with Coulomb islands of colloidal Au nanoparticles covered by organic alkanethiol molecules, the hybrid passivated SETs showed clear and stable Coulomb diamonds with applied top-gate voltage [Citation36].

Here, we report three-input gate logic operations on a single chemically assembled SET with hybrid passivated bilayers based on mixed SAMs and pulsed laser deposited (PLD) aluminum oxide (AlO). The top-gate electrode was prepared on a high-k material of an AlO

passivation layer. The chemically assembled SET consists of a Au nanoparticle Coulomb island, top-gate electrodes together with two side-gate electrodes (with clear Coulomb blockade behavior), and Coulomb diamonds for all three-input gates at 9 K. XOR logic operations with the three-input gates are demonstrated by applying simultaneous pulse gate voltages. These results extend the possibility of combining top-down and bottom-up adoption technologies for the fabrication of chemically assembled SET logic circuits, in which organic alkanethiols and inorganic materials are used as hybrid insulators.

2. Experimental details

The chemically assembled SET used in this paper was fabricated through a combination of top-down and bottom-up methods based on previous studies [Citation21–Citation23]. Electrode patterns were designed by EBL (Elionix, ELS-7500EX, Hachioji, Japan) on a SiO (300 nm)/Si substrate, and a Ti/Au layer was evaporated onto the substrate under high vacuum conditions. At this point, the average gap separation is approximately 25 nm. Probing electrodes were then added by photolithography, and an iodine electroless Au plating solution was used to reduce the size of the nanogaps to less than 5 nm via a self-termination mechanism [Citation26–Citation28]. Chemically synthesized decanethiol-protected Au nanoparticles with a core diameter of 6.2

0.8 nm were then chemisorbed between the nanogap electrodes using decanedithiol and octanethiol mixed self-assembled monolayers (SAMs) on the nanogap electrodes [Citation38–Citation43].

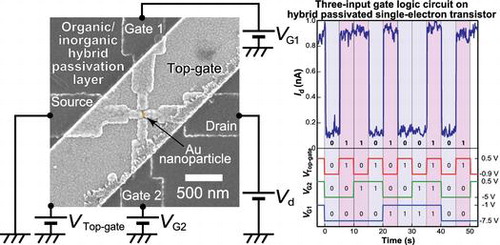

In this study, we introduce alkanethiol/alkanedithiol mixed SAM and inorganic AlO as hybrid passivation materials. The top view scanning electron microscopy (SEM) image of the three-input gate SET is shown in Figure (a). An AlO

layer (50 nm) was deposited at room temperature by PLD [Citation44]. Finally, Ti/Au (30 nm/70 nm) top-gate electrodes were added using an EBL-based overlay method with a poly(methyl methacrylate) resist layer applied with pre-baking at 423 K for 10 min [Citation36,Citation45]. As shown in Figure (a), the top-gate electrodes fully cover the nanogap area, where Coulomb islands of chemically anchored colloidal Au nanoparticles exist beneath the hybrid passivation layer. We can clearly observe the source and drain electrodes along with the two side-gates (gate 1 and gate 2) and the top-gate. A cross-sectional schematic diagram of the final SET is shown in Figure (b).

Figure 1. (a) SEM top-view image of hybrid passivated chemically assembled SET with two side-gates (1 and 2), and one top-gate. (b) Cross-sectional image of the hybrid SAM and AlO-passivated chemically assembled SET with a gold top-gate electrode. (c) Equivalent circuit of the SET with a Coulomb island comprised of a 6.2-nm-diameter chemically synthesized Au nanoparticle, two side-gate electrodes (1 and 2), and one top-gate electrode. The SET parameters are as follows:

, the tunneling resistance between the source electrode and the Au core of the nanoparticle;

, the tunneling resistance between the drain electrode and the Au core;

, the capacitance between the source electrode and the Au core;

, the capacitance between the drain electrode and the Au core;

, the side-gate 1 capacitance;

, the side-gate 2 capacitance;

, the top-gate capacitance.

The electron transport properties of the SET were measured using a mechanical refrigerator-type probe (Nagase, GRAIL10-LOGOS01S, Nihonbashi, Japan) and asemiconductor device analyzer (B1500, Agilent, Santa Rosa, CA, USA). The measurement temperature was 9 K. All measurements were conducted under the same conditions as in previous studies [Citation21–Citation23]. The vacuumpressure in the measurement chamber was approximately Pa. The stability diagram of the two-dimensional d

/d

plot was acquired by differentiating the

–

curve numerically. Finally, the logic operation was demonstrated by applying simultaneous three-input gate pulse voltages and observing the

current response.

3. Results and discussion

Drain current vs. drain voltage (–

) characteristics of chemically assembled SETs with both the hybrid passivation due to SAMs and AlO

, and top-gate electrodes under top-gate voltages (

) of 0.3 and 1.5 V, are shown in Figure . Clear Coulomb staircases were observed at 9 K. The theoretical curves at offset charges

of 0 and 0.5e (e: unit charge) were fitted to the experimental results using the orthodox model [Citation46,Citation47]. The evaluated SET parameters of

,

,

and

are 1.6 M

, 6.5 M

, 2.9 aF, and 2.9 aF, respectively (Figure (c)). Two theoretical curves coincide well with the experimental Coulomb staircases, indicating that the hybrid SAM and AlO

passivated SET still functioned after the PLD and EBL processes for the passivation and top-gate electrode, respectively, during which the sample was pre-baked at 423 K for 10 min within the EBL process.

Figure 2. Experimental results of curves for different gate voltages of

=0,

=0 and

=1.5 V (red open circle), and

=0,

=0 and

=0.3 V (black open circle) at 9 K. Theoretical

curves obtained from the orthodox model at different fractional charges

of 0.5e (red solid line) and 0 (black solid line). The other evaluated SET parameters of

,

,

and

are 1.6 M

, 6.5 M

, 2.9 aF, and 2.9 aF, respectively. The coordinate origins are shifted to 2.5 nA (red open circle and red solid line) and –2.5 nA (black open circle and black solid line) for clarity.

Figure 3. Experimental Coulomb oscillations under the application of (a) side-gate 1 voltage ,

=

=0 V, (b) side-gate 2 voltage

,

=

=0 V, and (c) top-gate voltage

,

=

=0 V with a drain bias voltage

of 15 mV at 9 K. Experimental stability diagrams under the application of (d) side-gate 1 voltage

,

=

=0 V, (e) side-gate 2 voltage

,

=

=0 V, and (f) top-gate voltage

,

=

=0 V at 9 K.

We then studied the drain current vs. gate voltages characteristics for each gate by applying a bias on gate 1 (), gate 2 (

), and the top-gate (

). Coulomb oscillations were clearly observed for the side-gates 1 and 2 and for the top-gate, as shown in Figure (a)–(c) respectively. In each case, a drain voltage

of 15 mV was chosen to simplify the comparison. When the peak voltage periods

of the Coulomb oscillations are 8.0, 7.4, and 2.5 V for

,

, and

, the gate capacitances of

,

-pagination

and were evaluated by

(e: unit charge) as 20, 22, and 63 zF, respectively.

is nearly identical to

and

is three times larger than

and

. The numeric values of

,

and

are large enough to achieve logic operation under bias voltages of up to 8 V for the three-input gates. It should be noted that the three gate capacitances can be adjusted to nearly identical values by adjusting the thickness of the passivation layer.

Figure 4. Experimental three-input gate exclusive OR (XOR) logic operation obtained with hybrid SAM and AlO-passivated chemically assembled SETs.

output current plot vs. time (blue solid line) under pulse voltages for the top-gate (red), side-gate 1 (blue) and second side-gate 2 (green). The height of the input pulse voltage for side-gate 1 is –7.5 V to –1 V, for side-gate 2 is –5 V to 0.5 V, and for the top-gate is –0.9 V to 0.5 V. Input-output table for three-gate XOR logic operation (inset).

We have previously reported two-input gate logic operation based on the SET without passivation materials and the values of two side-gate capacitances were 28 and 38 zF, respectively [Citation31]. Larger side-gate capacitances are strongly expected by the high-k passivation material of with AlO; however, the values of

-pagination (= 20 zF) and

(=22 zF) are almost comparable with the previous results [Citation31]. As shown in the SEM image in Figure (a), the width of the source and the drain electrodes at the gap is almost 70 nm and the gap separation is 3 nm. Consequently, the electric flux from the side-gate electrodes to Au nanoparticle (6.2 nm in core diameter) tends to be shielded by source and drain electrodes. Conversely, the gap separation of the previous two-input gate SET was as large as 7 nm and the hemispherical source and drain electrode structures were observed at the gap [Citation31]. As a result, larger side-gate capacitances are expected on three-input gates SETs with the hybrid passivation bilayer by extending the gap separation and by reducing the width of the source and the drain electrodes, especially at the gap.

The stability diagrams for each gate (gate 1, gate 2, and top-gate) of the device were then measured at 9 K, as shown in Figure (d)–(f), respectively. The uniform Coulomb diamond shape is clearly observed for the three gate voltages in Figure (d)–(f). Consequently, the offset charges of the Coulomb islands equally oscillate from gate 1, gate 2, and the top-gate electrodes based on their gate capacitances.

There are 90 SETs on the one sample. After the introduction of the hybrid passivation materials and the top-gate electrode, stable Coulomb diamonds were observed in 13 out of 90 SETs. Within the 13 SETs, five SETs have a single Coulomb island of an Au nanoparticle, which is judged by periodical and uniform Coulomb diamond shape. All experimental results of this paper originate from the same SET with the comparable two side-gate capacitances, which were selected from the five SETs.

The charging energy of this SET is given as , where

, and is evaluated as 14 meV. We have examined the dependence of

on the Au core diameter in chemically assembled SETs by introducing a concentric sphere model, and the typical

for a core diameter of 6.2 nm is 38 meV [Citation22,Citation48]. An

value of 14 meV in the hybrid SAM and AlO

passivated chemically assembled SET is nearly three times smaller than that in the chemically assembled SET without the hybrid passivation bilayer. This decrease in

likely results from the PLD AlO

passivation material, having a relative permittivity of about 8 [Citation49]. Considering the relative permittivity of alkanethiol protecting molecules (2.6 [Citation50]), the passivation material AlO

should cover and fill the surrounding space of both the Coulomb island of alkanethiol protected Au nanoparticles and the nanogap regions.

We have previously reported the uniform charging energy of the SETs without the AlO passivation material [Citation22]. It can be noted that the uniform charging energy of 14 meV was also observed on the five SETs originating from a single Au nanoparticle even after the introduction of the hybrid passivation bilayer and the top-gate electrodes.

The measurement sequence of Coulomb oscillation and Coulomb diamonds was top-gate, gate 1, and gate 2. Within the Coulomb oscillation and Coulomb diamonds for gate 2 (Figure (b) and (e)), the current peak voltage moved to the right compared with those for top-gate and gate 1. This peak shift value is attributed to the change in , whose value is evaluated as 0.3e. As shown in Figure (d) and (f), the stable Coulomb diamonds were clearly observed, which means that

did not change during those measurements. As a result, the change in

happened during the measurements interval between gate 1 (Figure (d)) and gate 2 (Figure (e)). It is noted that

kept the constant value after this change throughout the measurement of the three gate pulse voltage as follows.

The results of XOR logic operation with three-input gate modulation on the same SET using SAM and AlO as the hybrid passivation bilayer are shown in Figure (a) and (b). Figure (a) shows the output current under the application of the three gate pulse voltages and a drain voltage of 25 mV. Figure (b) shows the experimental pulse sequence of three-input gate voltages vs. time with the table of the three-input XOR gate, in which ‘1’ refers to the ON state with current flow and ‘0’ is the OFF state with low current. For side-gate 1 (blue solid line), side-gate 2 (green line), and top-gate (red line), the OFF states are –7.5, –5.0 and –0.9 V and the ON states are –1, 0.5, and 0.5 V, respectively. Depending on the three-input gate voltages, the output current varied between 0.9 and 0.12 nA, which are defined as ON and OFF states (Figure (a)). Times between 0 and 5 s (input state: 0, 0, and 0) correspond to the beginning of the output in the table (output state: 0). We obtained the correct XOR logic output for each input step, as the ON state of the output current appears only when the sum of the ON state inputs is an odd number.

The ON/OFF ratio of three-input XOR logic is 7.5, which is almost one order of magnitude in difference. The output ON and OFF current are approximately 900 and 120 pA, respectively. We have previously reported two-input chemically assembled SET logic circuit operation in which the ON/OFF ratio and OFF current were and 0.1 pA, respectively [Citation31]. A large OFF current of 120 pA under

of 25 mV is due to almost outside of Coulomb blockade region; however, we have only tried to measure three-input gate XOR logic operation under

of 25 mV. Based on the experimental Coulomb staircases at ON (

= 0.5e) and OFF (

= 0) states in Figure , ON and OFF currents under

of 15 mV were 900 and 0.7 pA, respectively. Consequently, ON/OFF ratio of

was expected by choosing

of 15 mV.

Due to the small side-gate capacitances of 20 and 22 zF, the gate voltages for the logic operation were slightly large, e.g. –5 V and –7.5 V. We are now trying to reduce the width of the source and drain electrodes at the gap comparable for the size of an Au nanoparticle, which will lead the lower-voltage operation by a geometry improvement.

4. Conclusions

We have demonstrated three-input gate XOR logic operation on chemically assembled SETs by introducing a hybrid SAM and AlO passivation bilayer. Based on the small charging energy and the large leakage current, the high-k material of a PLD AlO

was found to fill the space surrounding the Au nanoparticles and the nanogap electrodes. Three-input XOR logic operation was stable and reproducible with an ON/OFF ratio of 7.5. This hybrid SAM and AlO

passivation is significant for the fabrication of sub-10-nm chemically assembled SETs to function as logic devices, since it enables connection to CMOS technologies via planar processes.

Acknowledgements

We thank Ms. M. Miyakawa for the technical support regarding our SEM studies.

Additional information

Funding

Notes

No potential conflict of interest was reported by the authors.

Present address: Department of Electrical and Electronic Engineering, Kobe University. Present address: Mitsubishi Chemical Group Science and Technology Research Center.

References

- The International Technology Roadmap for Semiconductors [Internet]. Available from: http://www.itrs2.net/. (2017 January 15)

- Likharev KK. Single-electron devices and their applications. Proc IEEE. 1999;87:606–632.

- Durrani ZAK. Single-electron devices and circuits in silicon. London: Imperial College; 2009.

- Rahman SFBA, Nakata D, Shiratori Y, et al. Boolean logic gates utilizing GaAs three-branch nanowire junctions controlled by Schottky wrap gates. Jpn J Appl Phys. 2009;48:06FD01--4.

- Muller CR, Worschech L, Hopfner P, et al. Monolithically integrated logic nor gate based on GaAs/AlGaAs three-terminal junctions. IEEE Electron Device Lett. 2007;28:859–861.

- Wu PC, Ye Y, Liu C, et al. Logic gates constructed on CdS nanobelt field-effect transistors with high-k HfO2 top-gate dielectrics. J Mater Chem. 2009;19:7296–7300.

- Worschech L, Harmann F, Kim TY, et al. Universal and reconfigurable logic gates in a compact three-terminal resonant tunneling diode. Appl Phys Lett. 2010;96:042112--3.

- Venkataratnam AK, Goel AK. Design and simulation of logic circuits with hybrid architectures of single-electron transistors and conventional MOS devices at room temperature. Microelectron J. 2008;39:1461–1468.

- Stone NJ, Ahmed H. Logic circuit elements using single-electron tunnelling transistors. Electron Lett. 1999;35:1883–1884.

- Uchida K, Koga J, Ohba R, et al. Programmable single-electron transistor logic for future low-power intelligent LSI: proposal and room-temperature operation. IEEE Trans Electron Devices. 2003;50:1623–1630.

- Ono Y, Fujiwara A, Nishiguchi K, et al. Manipulation and detection of single electrons for future information processing. Jpn J Appl Phys. 2005;97:031101--19.

- Kim SJ, Lee CK, Chung RS, et al. Single-electron-based flexible multivalued exclusive-or logic gate. IEEE Trans Electron Devices. 2009;56:1048–1055.

- Kim JB, Hong SJ, Kim J. New circuits for XOR and XNOR functions. Int J Electron. 1997;82:131–143.

- He J, Durrani ZAK, Ahmed H. Two-way switch for binary decision diagram logic using silicon single-electron transistors. Microelectron Eng. 2004;73–74:712–718.

- Iwamura H, Akazawa M, Amemiya Y. Single-electron majority logic circuits. IEICE Trans Electron. 1998;E81C:42–48.

- Tsimperidis I, Karafyllidis I, Thanailakis A. A single-electron three-input AND gate. Microelectron J. 2002;33:191–195.

- Heij CP, Hadley P, Mooij JE. Single-electron inverter. Appl Phys Lett. 2001;78:1140–1142.

- Noguchi Y, Yamamoto M, Ishii H, et al. Photoresponses in gold nanoparticle single-electron transistors with molecular floating gates. Jpn J Appl Phys. 2013;52:110102--7.

- Takahashi Y, Fujiwara A, Yamazaki K, et al. Multigate single-electron transistors and their application to an exclusive-OR gate. Appl Phys Lett. 2000;76:637–639.

- Tsuya D, Suzuki M, Aoyagi Y, et al. Exclusive-OR gate using a two-input single-electron transistor in single-wall carbon nanotubes. Appl Phys Lett. 2005;87:153101–3.

- Azuma Y, Yasutake Y, Kono K, et al. Single-electron transistor fabricated by two bottom-up processes of electroless Au plating and chemisorption of Au nanoparticle. Jpn J Appl Phys. 2010;49:090206–3.

- Okabayashi N, Maeda K, Murak T, et al. Uniform charging energy of single-electron transistors by using size-controlled Au nanoparticles. Appl Phys Lett. 2012;100:033101--3.

- Azuma Y, Suzuki S, Maeda K, et al. Nanoparticle single-electron transistor with metal-bridged top-gate and nanogap electrodes. Appl Phys Lett. 2011;99:073109--3.

- Kano S, Azuma Y, Tanaka D, et al. Random telegraph signals by alkanethiol-protected Au nanoparticles in chemically assembled single-electron transistors. J Appl Phys. 2013;114:223717--6.

- Azuma Y, Sakamoto M, Teranishi T, et al. Memory operations in Au nanoparticle single-electron transistors with floating gate electrodes. Appl Phys Lett. 2016;109:223106--5.

- Yasutake Y, Kono K, Kanehara M, et al. Simultaneous fabrication of nanogap gold electrodes by electroless gold plating using a common medical liquid. Appl Phys Lett. 2007;91:203107-3.

- Serdio VVM, Azuma Y, Takeshita S, et al. Robust nanogap electrodes by self-terminating electroless gold plating. Nanoscale. 2012;4:7161–7167.

- Serdio VVM, Muraki T, Takeshita S, et al. Gap separation-controlled nanogap electrodes by molecular ruler electroless gold plating. RSC Adv. 2015;5:22160–22167.

- Azuma Y, Onuma Y, Sakamoto M, et al. Rhombic Coulomb diamonds in a single-electron transistor based on an Au nanoparticle chemically anchored at both ends. Nanoscale. 2016;8:4720–4726.

- Kano S, Azuma Y, Maeda K, et al. Ideal discrete energy levels in synthesized Au nanoparticles for chemically assembled single-electron transistors. ACS Nano. 2012;6:9972–9977.

- Maeda K, Okabayashi N, Kano S, et al. Logic operations of chemically assembled single-electron transistor. ACS Nano. 2012;6:2798–2803.

- Ponce Ortiz R, Facchetti A, Marks TJ. High-k organic, inorganic, and hybrid dielectrics for low-voltage organic field-effect transistors. Chem Rev. 2010;110:205–239.

- Klauk H, Zschieschang U, Pflaum J, et al. Ultralow-power organic complementary circuits. Nature. 2007;445:745–748.

- Klauk H, Zschieschang U, Weitz RT, et al. Organic transistors based on di(phenylvinyl)anthracene: performance and stability. Adv Mater. 2007;19:3882–3887.

- Wöbkenberg PH, Ball J, Kooistra FB, et al. Low-voltage organic transistors based on solution processed semiconductors and self-assembled monolayer gate dielectrics. Appl Phys Lett. 2008;93:013303--3.

- Hackenberger G, Azuma Y, Kano S, et al. Silicon-nitride-passivated bottom-up single-electron transistors. Jpn J Appl Phys. 2013;52:110101--5.

- Maehashi K, Ohno Y, Inoue K, et al. Electrical characterization of carbon nanotube field-effect transistors with SiNx passivation films deposited by catalytic chemical vapor deposition. Appl Phys Lett. 2008;92:183111--3.

- Teranishi T, Hasegawa S, Shimizu T, et al. Heat-induced size evolution of gold nanoparticles in the solid state. Adv Mater. 2001;13:1699–1701.

- Shimizu T, Teranishi T, Hasegawa S, et al. Size evolution of alkanethiol-protected gold nanoparticles by heat treatment in the solid state. J Phys Chem B. 2003;107:2719–2724.

- Kanehara M, Sakurai J, Sugmura H, et al. Room-temperature size evolution of thiol-protected gold nanoparticles assisted by proton acids and halogen anions. J Am Chem Soc. 2009;131:1630–1631.

- Li X, Yasutake Y, Kono K, et al. Au nanoparticles chemisorbed by dithiol molecules inserted in alkanethiol self-assembled monolayers characterized by scanning tunneling microscopy. Jpn J Appl Phys. 2009;48:04C180-4.

- Kano S, Azuma Y, Kanehara M, et al. Room-temperature Coulomb blockade from chemically synthesized Au nanoparticles stabilized by acid-base interaction. Appl Phys Express. 2010;3:105003--3.

- Koo H, Kano S, Tanaka D, et al. Characterization of thiol-functionalized oligo(phenylene-ethynylene)-protected Au nanoparticles by scanning tunneling microscopy and spectroscopy. Appl Phys Lett. 2012;101:083115--5.

- Matsuzaki K, Nomura K, Yanagi H, et al. Epitaxial growth of high mobility Cu2O thin films and application to p-channel thin film transistor. Appl Phys Lett. 2008;93:202107--3.

- Choi DH, Wang Q, Azuma Y, et al. Fabrication and characterization of fully flattened carbon nanotubes: a new graphene nanoribbon. Sci Rep. 2013;3:1617--5.

- Hanna AE, Tinkham M. Variation of the Coulomb staircase in a two-junction system by fractional electron charge. Phys Rev B. 1991;44:5919–5922.

- Zhang H, Yasutake Y, Shichibu Y, et al. Tunneling resistance of double-barrier tunneling structures with an alkanethiol-protected Au nanoparticle. Phys Rev B. 2015;72:205441--7.

- Kano S, Tanaka D, Sakamoto M, et al. Control of charging energy in chemically assembled nanoparticle single-electron transistors. Nanotechnology. 2015;26:045702--9.

- Ion M, Berbecaru C, Iftimie S, et al. PLD deposited Al2O3 thin films for transparent electronics. Dig J Nanomater Bios. 2012;7:1609–1614.

- Majima Y, Ogawa D, Iwamoto M, et al. Negative differential resistance by molecular resonant tunneling between neutral tribenzosubporphine anchored to a Au(111) surface and tribenzosubporphine cation adsorbed on to a tungsten tip. J Am Chem Soc. 2013;135:14159–14166.