?Mathematical formulae have been encoded as MathML and are displayed in this HTML version using MathJax in order to improve their display. Uncheck the box to turn MathJax off. This feature requires Javascript. Click on a formula to zoom.

?Mathematical formulae have been encoded as MathML and are displayed in this HTML version using MathJax in order to improve their display. Uncheck the box to turn MathJax off. This feature requires Javascript. Click on a formula to zoom.Abstract

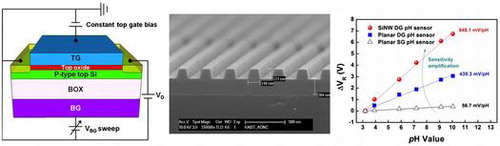

This work describes the construction of a sensitive, stable, and label-free sensor based on a dual-gate field-effect transistor (DG FET), in which uniformly distributed and size-controlled silicon nanowire (SiNW) arrays by nanoimprint lithography act as conductor channels. Compared to previous DG FETs with a planar-type silicon channel layer, the constructed SiNW DG FETs exhibited superior electrical properties including a higher capacitive-coupling ratio of 18.0 and a lower off-state leakage current under high-temperature stress. In addition, while the conventional planar single-gate (SG) FET- and planar DG FET-based pH sensors showed the sensitivities of 56.7 mV/pH and 439.3 mV/pH, respectively, the SiNW DG FET-based pH sensors showed not only a higher sensitivity of 984.1 mV/pH, but also a lower drift rate of 0.8% for pH-sensitivity. This demonstrates that the SiNW DG FETs simultaneously achieve high sensitivity and stability, with significant potential for future biosensing applications.

1. Introduction

In recent years, the demand for biosensors has increased rapidly because of aging societies. In particular, label-free biosensors based on field-effect transistors (FETs) have attracted considerable attention as potential candidates for point-of-care biosensing applications, having numerous merits such as rapid label-free detection, miniaturized sensor size, and portability.[Citation1–6] During the development of high-quality and reliable FET-based biosensors, sensitivity and stability are among the most important factors under consideration. However, achieving both sensitivity and stability simultaneously is difficult because of the trade-off relationship between these properties.[Citation7] Stability is generally influenced by changes in the sensitivity. When signal amplitude is increased by amplification circuits or by enlarging the sensor surface area, the noise in the system is increased as well, and no enhancement of the signal-to-noise (S/N) ratio occurs.

In order to attain an optimum balance between sensitivity and stability, and thereby increase the S/N ratio, dual-gate FETs (DG FETs) have been developed.[Citation8–10] DG FETs can amplify the signal by several times through a capacitive-coupling effect, which is induced by their unique asymmetric structure between the top and bottom gates.[Citation11] In our previous works, we have already demonstrated that the S/N ratio is ultimately enhanced because DG FETs amplify the signal relatively more largely than the noise.[Citation12–14] However, DG FETs still have some room for further improvement of their performance.

Silicon nanowire-based FETs (SiNW FETs) have recently drawn attention as promising biosensor tools because of their ultrahigh sensitivity, selectivity, and size compatibility.[Citation15–17] SiNW FETs offer an increased capacitance in their nanowire geometry as well as an outstanding charge controllability and a low off-state leakage current due to their high surface-area-to-volume ratios.[Citation18–21] Nevertheless, the availability of SiNW FETs is limited by the difficulty of the manufacturing process for the devices. Fabrication of SiNW FETs follows a bottom-up or top-down approach. SiNW bottom-up growth processes, such as the vapor-liquid-solid (VLS) growth technique, plasma-enhanced chemical vapor deposition (PECVD), and layer-by-layer self-assembly, face difficulties in device integration because the size and positions of the SiNWs cannot always be perfectly controlled. Top-down approaches, such as electron-beam lithography, focused-ion-beam lithography, and deep-UV photolithography, allow SiNW printing to obtain the desired shapes and structures, but are limited by low throughput and high cost because of the serial ‘writing’ processing and the use of expensive instrumentation; hence, such devices are limited to use in research settings.[Citation22]

Nanoimprint lithography (NIL) is a simple nanolithography process that transfers patterns by pressing a designed master mold into the resist; this technique has been proposed to overcome the limited production volume and high cost of other top-down techniques.[Citation23] Compared to conventional nanopatterning techniques, NIL has higher throughput, lower fabrication cost, and excellent reproducibility.[Citation24,25] Moreover, it can be used to fabricate not only uniformly distributed and size-controlled nanowires over a large area but also various high-resolution nanoscale patterns.[Citation26]

Here, we design DG FETs based on SiNWs formed using NIL and compare the performance of these devices with conventional planar DG FETs. By applying the DG FETs in pH sensors, we investigate the potential of SiNW DG FETs in future biological and chemical sensors.

2. Experimental section

2.1. Formation of SiNW on semiconductor-on-insulator (SOI) wafer

The fabrication process of SiNWs is shown in Figure (a). A p-type (100) silicon-on-insulator (SOI) wafer with a 200-nm-thick buried oxide (BOX) layer was used as the base substrate. The thickness of the top silicon layer of the SOI wafer was ~120 nm and the resistivity and doping level were 10 Ω cm and 1 × 1015 cm−3, respectively. The substrate was cleaned in acetone and isopropanol for 10 min and rinsed with deionized water for 5 min, before drying with nitrogen. To decrease the hydrophobicity of the substrate, it was treated with oxygen plasma (PINK GmbH, Wertheim, Germany, plasma-finish) for 10 s at 300 W, pressure of 80 Pa, and an O2 gas flow rate of 300 ml min–1. A 200-nm-thick poly(methyl methacrylate) (PMMA) (Micro resist, Berlin, Germany, PMMA35k300) layer was spin-coated onto the glass substrate of the control sample at 3000 rpm for 30 s and baked at 120°C for 120 s using a hot plate. A polycarbonate (PC) film mold was pressed using a nanoimprinter at 4.5 bar for 140 min. The transfer temperature was 130°C, above the glass transition temperature Tg of PMMA. The PC film mold and the imprinted polymer were cooled below Tg of the polymer to preserve the imprinted pattern after mold release at 90°C. The thermal resin layer formed by the imprinted linear arrays was successfully formed on the substrate. After imprinting, inductively coupled plasma (ICP) dry etching of Si using Cl2 (20 sccm)/Ar (40 sccm) plasma (Oxford Plasmalab, Bedford, USA 100) was performed with a pressure of 3 mTorr and source and bias powers of 1000 W (top) and 400 W (bottom), respectively. The remaining PMMA layer was removed by an acetone solution under sonication. Figure (b) and 1(c) show scanning electron microscopy (SEM) images of the SiNWs formed by NIL.

2.2. Fabrication of the FET-based sensor

FET-based sensors were designed using standard metal-oxide semiconductor field-effect transistors (MOSFETs) and contained a FET and sensing membrane as transducer and sensing regions, respectively.[Citation27] In this work, we separated the sensing membrane from the FET to allow the reusability of the FET, disposability of the sensing membrane, and minimization of ion damage to the FET caused by undesirable ions on the sensing membrane.[Citation28]

2.2.1. Fabrication of SiNW FET (transducer region)

Figure (a) shows a flow diagram of the fabrication of SiNW FETs. SiNWs formed by NIL were used for the channel layer of the FET. After forming an active region by photolithography and a reactive ion etching (RIE) process, a 100-nm-thick phosphorus-doped polycrystalline silicon (N+ poly-Si) was deposited at the source and drain regions using low-pressure chemical vapor deposition (LPCVD). Next, a 20-nm-thick SiO2 layer for the top-gate oxide (Tox) was grown by thermal oxidation. To reduce the defect density and improve the electrical properties of the devices, rapid thermal annealing (RTA) was performed at 850°C for 30 s in N2/O2 ambient gas. A 150 nm-thick aluminum gate electrode was formed using an e-beam evaporator. Finally, forming gas annealing was performed at 400°C for 30 min in 2% H2/N2 ambient to improve the interfacial quality between the top/bottom gate oxides and channel layer. The channel length and width of the fabricated FET were 10 μm and 20 μm, respectively. An optical microscope image of the fabricated SiNW FETs is shown in Figure (b).

2.2.2. Fabrication of the sensing membrane (sensing region)

A 100-nm-thick indium tin oxide (ITO) metal electrode, for transferring surface potential variations on the sensing membrane to the gate electrode of the FET, was deposited on a glass substrate using a radio-frequency (RF) sputter process. Subsequently, a 50-nm-thick tin oxide (SnO2) layer was deposited by RF magnetron sputtering at room temperature. SnO2 was used as the sensing membrane because previous studies have demonstrated the exceptional long-term stability and reliability of the material.[Citation29,30] During sputtering, the RF power, chamber pressure, and Ar gas flow rate were maintained at 50 W, 3 mTorr, and 20 sccm, respectively. Finally, a polydimethylsiloxane (PDMS) chamber for the injection of the pH solution was attached to the sensing membrane using silicone glue. The inside diameter of the active region in the chamber was 0.6 cm. The ITO electrode in the sensing region was directly connected to the aluminum gate electrode in the transducer region using an electric wire. A schematic of the fabricated SiNW FET-based sensor and a photograph of the sensing region are shown in Figure (c) and 2(d), respectively.

2.3. Operational mechanism of the DG FET-based sensor

The fabricated FET-based sensors could be operated in both single-gate (SG) and dual-gate (DG) modes (Figure S1). Conventional FET-based sensors are generally driven in SG mode with the maximum achievable sensitivity, or Nernstian sensitivity, limited to 59 mV/pH at 25°C, because sensitivity () is determined only by changes in the surface potential (Δψ0) of the sensing membrane, which can be described as

.[Citation16,31] The FET-based sensors proposed in this study are driven in DG mode; the sensitivity (

) depends not only on but also on the capacitive-coupling ratio (Ctop/Cbottom), representing the amplification factor of the sensor, between the top and bottom gate capacitances; this can be described as follows:

where Ctop and Cbottom denote the top and bottom gate capacitances per unit area, respectively.[Citation13,32] Consequently, the DG FET-based sensor can achieve highly enhanced sensitivity, exceeding the Nernst limit of 59 mV/pH, if Ctop is much greater than Cbottom.

2.4. Measurement of the FET-based sensor

The drain current versus gate voltage (ID-VG) curves in the electrical characteristics evaluation and the pH sensing test were measured by an Agilent 4156B semiconductor parameter analyzer. A commercial Ag/AgCl electrode was used as the reference electrode; all measurements were conducted in a dark box to avoid interference by light and external noise.

3. Results and discussion

3.1. Electrical characteristics of the fabricated FETs

Figure depicts (a) the transfer behavior (ID-VG) and (b) the output characteristic (ID-VD) curves of the fabricated planar and SiNW FETs. As observed from the transfer behavior, both devices have strong gate dependences. In addition, the output characteristics show that the drain current is effectively controlled by several constant gate bias voltages (VG from 0 to 2 V with a step of 0.25 V). The extracted electrical parameters are summarized in Table . Compared to the planar FETs, the SiNW FETs exhibit superior electrical characteristics, including a higher field-effect mobility of 730.3 cm2 V–1 s–1, lower threshold voltage (Vth) of 54.7 mV, steeper subthreshold swing (SS) of 76.0 mV/dec, larger on/off current ratio of 2.3 × 108, and lower interface trap density (Dit) of 2.8 × 1012 cm−2 eV−1. Dit between the top silicon channel and top oxide was calculated by:

Figure 3. (a) Transfer behavior for constant VD (50 mV and 1 V) of planar FETs and SiNW FETs. (b) Electrical output characterization of planar FETs and SiNW FETs. The gate voltage is varied from 0 to 2 V in steps of 0.25 V.

Table 1. Electrical parameters of planar and SiNW FETs.

where Ci denotes the capacitance per unit area, q is the electron charge, kB is the Boltzmann’s constant, and T is the absolute temperature.

3.2. Signal amplification capabilities of the FETs in DG operation

Figure (a) depicts a schematic of planar and SiNW FETs in DG operation (hereafter, referred to as planar or SiNW DG FETs). To compare the signal amplification capabilities of the devices in DG mode, we observed the ID-VG curves with varying the top gate bias from –600 mV to 600 mV in steps of 60 mV. Figure (b) and 4(c) show the ID-VG curves of the planar and SiNW DG FETs as functions of the top gate bias. In both devices, is shifted to the negative direction as the top gate bias is changed from –600 mV to 600 mV. This is because the top surface region of the p-type top silicon layer is depleted by the electrons induced by the positive top-gate bias; near the region, a negative-charged space-charge region is developed that assists with channel formation during bottom-gate sweeping.[Citation10,33,34]

Figure 4. (a) Schematic of FETs in dual-gate (DG) operation. Transfer curves of (b) planar DG FETs and (c) SiNW DG FETs with constant top gate biases from –600 mV to 600 mV in steps of 60 mV, as indicated by the arrow. The drain bias is 50 mV. (d) Top gate bias versus plot for planar and SiNW DG FETs.

for each top gate bias is defined as the bottom-gate voltage corresponding to ID of 1 nA.

Figure (d) shows the variation of for planar and SiNW DG FETs as a function of top-gate bias variation. The ratios of the top-gate bias to

variation, or the capacitive-coupling ratios, for the planar and SiNW DG FETs are 9.1 and 18.0 respectively. The SiNW DG FETs have higher capacitive-coupling ratios than planar DG FETs because the former has a larger top surface area and smaller bottom surface area, leading to an increase in Ctop and a decrease Cbottom (Figure S2).

3.3. Stability test of the devices under high-temperature stress

In order to evaluate the stability of the planar and SiNW FETs, we observed the electrical performances of the devices under high-temperature stress. Figure shows the ID-VG curves of planar and SiNW DG FETs measured at 120°C. Here, an interesting phenomenon is observed in the results: planar DG FETs have large off-state leakage currents with increases in the top gate, but SiNW DG FETs show no corresponding leakage. The off-state leakage current in the planar DG FETs is attributed to the many electrons, generated by the high-temperature stress, forming a surface inversion region that acts as a leakage current path, as shown in Figure (c)(i) in the top silicon channel layer. In contrast, in the SiNW DG FETs, no surface inversion region is developed because the energy of the top gate bias is distributed over a wide surface area of SiNWs, as shown in Figure (c)(ii) (supplementary data are shown in Figure S3).

Figure 5. ID-VG curves for (a) planar DG FETs and (b) SiNW DG FETs measured at 120°C with constant top gate biases ranging from –600 mV to + 600 mV in steps of + 60 mV as indicated by the arrow. The drain bias is set at 50 mV. (c) Schematic illustration of the operation principle of a planar DG FET and SiNW DG FET measured at 120°C with constant top gate bias of + 600 mV. (d) Top gate bias versus plot of planar DG FETs and SiNW DG FETs measured at 120°C.

Figure (d) displays the variation for planar and SiNW DG FETs as functions of the top gate bias variation measured at 120°C. The capacitive-coupling ratios of the planar and SiNW DG FETs are shown to be 11.1 and 18.4, respectively. Table summarizes the capacitive-coupling ratios of the planar and SiNW DG FETs, measured at room temperature and 120°C. SiNW DG FETs exhibit a small error percentage of 2.6%, whereas planar DG FETs have a relatively larger error of 22.2%. This implies that the SiNW DG FETs have better stability and reliability than the planar DG FETs do.

Table 2. Capacitive-coupling ratios of planar and SiNW DG FETs measured at room temperature and 120°C.

3.4. pH sensing test

Figure shows the ID-VG curves of (a) planar SG FET-based pH sensors (hereafter referred to as planar SG pH sensors), (b) planar DG pH sensors, and (c) SiNW DG pH sensors, measured in solutions with different pH values. As shown, Vth is positively shifted for all pH sensors, with shifting behavior based on the variation in pH between 3 and 10. Figure (d) shows the change in the response voltage (VR) of the planar and SiNW pH sensors based on the pH variation. As shown, while the planar SG pH sensors have a low sensitivity of 56.7 mV/pH within the Nernst limit of 59 mV/pH, the planar DG pH sensors exhibit a high sensitivity of 439.3 mV/pH, far beyond the conventional pH response limit. In particular, the sensitivity (984.1 mV/pH) of the SiNW DG pH sensors is amplified significantly more than that of the conventional planar DG pH sensors, because they have such high capacitive-coupling ratios. The measured sensing parameters are summarized in Table (ID-VG curves of SiNW SG pH sensors are shown in Figure S4).

Figure 6. ID-VG curves of (a) planar SG pH sensors, (b) planar DG pH sensors, and (c) SiNW DG pH sensors for a large pH range (3–10). All measurements performed at VD = 50 mV and conducted three times to verify the reproducibility. (d) Change in the response voltage (VR) of planar and SiNW pH sensors for a wide range of pH (3–10). VR for each pH buffer solution defined as a corresponding gate voltage to reference drain current (IR) of 1 nA.

Table 3. Sensing parameters of planar and SiNW pH sensors measured in each operation mode.

In order to evaluate the long-term chemical stability of the fabricated pH sensors, we investigated the drift characteristics by observing the shift of Vth in a buffer solution of pH 7 over a period of 10 h. Figure shows the drift characteristics of the planar and SiNW pH sensors under SG and DG operation. SiNW pH sensors show relatively lower drift rates of 1.8 mV h–1 in SG mode and 8.3 mV h–1 in DG mode than those of the planar pH sensors, at 1.9 mV h–1 in SG mode and 8.0 mV h–1 in DG mode. To compare the drift rates for each pH sensor in SG and DG mode, the percentage of variation in the drift rate for the respective pH-sensitivity was considered. The results show that the SiNW DG pH sensors have the lowest drift rate for a pH sensitivity of 0.8%, implying that they have better long-term chemical stability than any other pH sensors tested here. The drift rates of the planar and SiNW pH sensors measured in each operation mode are summarized in Table .

4. Conclusions

In this study, we developed SiNW DG FETs and compared them with conventional planar DG FETs. Compared to the planar DG FETs, SiNW DG FETs showed not only a higher capacitive-coupling ratio but also a lower off-state leakage current under high-temperature stress. Furthermore, when the SiNW DG FETs were applied in pH sensors, they exhibited a highly enhanced sensitivity of 984.1 mV/pH, exceeding the Nernst limit, and a considerably superior stability characterized by a drift rate of less than 1%. For detecting the potential variation on the sensor surface, the FET-based sensors demonstrated here can be used as potential biological/chemical sensors, beyond applications in pH sensors.[Citation35,36] Thus, we expect that the SiNW DG FET sensor proposed here could be developed into a promising label-free sensor for various biological events, such as enzyme−substrate reactions, antigen−antibody bindings, and nucleic acid hybridizations.

Disclosure statement

No potential conflict of interest was reported by the authors.

Funding

This research was financially supported by the Basic Science Research Program through the National Research Foundation of Korea (NRF) funded by the Ministry of Education, Science and Technology [number 2013R1A1A2A10011202, 2014R1A2A1A11050768] and by the Technology Innovation Program [10060155] funded By the Ministry of Trade, industry & Energy (MI, Korea) and the KRIBB Initiative Research Program (KRIBB, Korea).

Supplemental data

The supplemental material for this paper is available online at https://doi.org/10.1080/14686996.2016.1253409

161021_2._STAM_Supplementary_data_CM160725_r2.docx

Download MS Word (664.2 KB)References

- Sarkar D, Liu W, Xie X, et al. MoS2 field-effect transistor for next-generation label-free biosensors. ACS Nano. 2014;8:3992–4003.10.1021/nn5009148

- Cai B, Wang S, Huang L, et al. Ultrasensitive label-free detection of PNA–DNA hybridization by reduced graphene oxide field-effect transistor biosensor. ACS Nano. 2014;8:2632–2638.10.1021/nn4063424

- Poghossian A, Schöning MJ. Label-free sensing of biomolecules with field-effect devices for clinical applications. Electroanalysis. 2014;26:1197–1213.10.1002/elan.201400073

- Kim SJ, Jung J, Lee KW, et al. Low-cost label-free electrical detection of artificial DNA nanostructures using solution-processed oxide thin-film transistors. ACS Appl Mater Interfaces. 2013;5:10715–10720.10.1021/am402857w

- Kim D-J, Sohn IY, Jung J-H, et al. Reduced graphene oxide field-effect transistor for label-free femtomolar protein detection. Biosens Bioelectron. 2013;41:621–626.10.1016/j.bios.2012.09.040

- Matsumoto A, Miyahara Y. Current and emerging challenges of field effect transistor based bio-sensing. Nanoscale. 2013;5:10702–10718.10.1039/c3nr02703a

- Schöning MJ, Tsarouchas D, Beckers L, et al. A highly long-term stable silicon-based pH sensor fabricated by pulsed laser deposition technique. Sens Actuators B Chem. 1996;35:228–233.10.1016/S0925-4005(97)80060-3

- Spijkman MJ, Myny K, Smits EC, et al. Dual-gate thin-film transistors, integrated circuits and sensors. Adv Mater Interfaces. 2011;23:3231–3242.10.1002/adma.201101493

- Jang H-J, Cho W-J. Performance enhancement of capacitive-coupling dual-gate ion-sensitive field-effect transistor in ultra-thin-body. Sci Rep. 2014;4:52–84.

- Lim H-K, Fossum JG. Threshold voltage of thin-film silicon-on-insulator (SOI) MOSFET's. IEEE Trans Electron Devices. 1983;30:1244–1251.

- Eminente S, Cristoloveanu S, Clerc R, et al. Ultra-thin fully-depleted SOI MOSFETs: special charge properties and coupling effects. Solid-State Electron. 2007;51:239–244.10.1016/j.sse.2007.01.016

- Lee I-K, Lee KH, Lee S, et al. Microwave annealing effect for highly reliable biosensor: dual-gate ion-sensitive field-effect transistor using amorphous InGaZnO thin-film transistor. ACS Appl Mater Interfaces. 2014;6:22680–22686.10.1021/am506805a

- Lee I-K, Jeun M, Jang H-J, et al. A self-amplified transistor immunosensor under dual gate operation: highly sensitive detection of hepatitis B surface antigen. Nanoscale. 2015;7:16789–16797.10.1039/C5NR03146J

- Jang H-J, Gu J-G, Cho W-J. Sensitivity enhancement of amorphous InGaZnO thin film transistor based extended gate field-effect transistors with dual-gate operation. Sens Actuators B Chem. 2013;181:880–884.10.1016/j.snb.2013.02.056

- Chen K-I, Li B-R, Chen Y-T. Silicon nanowire field-effect transistor-based biosensors for biomedical diagnosis and cellular recording investigation. Nano Today. 2011;6:131–154.10.1016/j.nantod.2011.02.001

- Knopfmacher O, Tarasov A, Fu W, et al. Nernst limit in dual-gated Si-nanowire FET sensors. Nano Lett. 2010;10:2268–2274.10.1021/nl100892y

- Kim K, Park C, Kwon D, et al. Silicon nanowire biosensors for detection of cardiac troponin I (cTnI) with high sensitivity. Biosens Bioelectron. 2016;77:695–701.10.1016/j.bios.2015.10.008

- Dorvel BR, Reddy B Jr, Go J, et al. Silicon nanowires with high-k hafnium oxide dielectrics for sensitive detection of small nucleic acid oligomers. ACS Nano. 2012;6:6150–6164.10.1021/nn301495k

- Fahad HM, Hussain MM. Are nanotube architectures more advantageous than nanowire architectures for field effect transistors? Sci Rep. 2012;2:475.

- Zheng G, Gao XP, Lieber CM. Frequency domain detection of biomolecules using silicon nanowire biosensors. Nano Lett. 2010;10:3179–3183.10.1021/nl1020975

- Larrieu G, Han X-L. Vertical nanowire array-based field effect transistors for ultimate scaling. Nanoscale. 2013;5:2437–2441.10.1039/c3nr33738c

- Shi S, Lu N, Lu Y, et al. Fabrication of periodic metal nanowires with microscale mold by nanoimprint lithography. ACS Appl Mater Interfaces. 2011;3:4174–4179.10.1021/am2010338

- Guo LJ. Nanoimprint lithography: methods and material requirements. Adv Mater Interfaces. 2007;19:495–513.10.1002/(ISSN)1521-4095

- Li Y, Zhang X, Wang D, et al. Fabricating sub-100 nm conducting polymer nanowires by edge nanoimprint lithography. J Colloid Interface Sci. 2015;458:300–304.10.1016/j.jcis.2015.07.067

- Ahn SH, Guo LJ. Large-area roll-to-roll and roll-to-plate nanoimprint lithography: a step toward high-throughput application of continuous nanoimprinting. ACS Nano. 2009;3:2304–2310.10.1021/nn9003633

- Mårtensson T, Carlberg P, Borgström M, et al. Nanowire arrays defined by nanoimprint lithography. Nano Lett. 2004;4:699–702.10.1021/nl035100s

- Bergveld P. Thirty years of ISFETOLOGY: what happened in the past 30 years and what may happen in the next 30 years. Sens Actuators B Chem. 2003;88:1–20.10.1016/S0925-4005(02)00301-5

- Yin L-T, Chou J-C, Chung W-Y, et al. Separate structure extended gate H+-ion sensitive field effect transistor on a glass substrate. Sens Actuators B Chem. 2000;71:106–111.10.1016/S0925-4005(00)00613-4

- Cheng Y, Xiong P, Yun CS, et al. Mechanism and optimization of pH sensing using SnO2 nanobelt field effect transistors. Nano Lett. 2008;8:4179–4184.10.1021/nl801696b

- Chi L-L, Chou J-C, Chung W-Y, et al. Study on extended gate field effect transistor with tin oxide sensing membrane. Mater Chem Phys. 2000;63:19–23.10.1016/S0254-0584(99)00184-4

- Chen S, Bomer JG, Carlen ET, et al. Al2O3/silicon nanoISFET with near ideal Nernstian response. Nano Lett. 2011;11:2334–2341.10.1021/nl200623n

- Spijkman M, Smits E, Cillessen J, et al. Beyond the Nernst-limit with dual-gate ZnO ion-sensitive field-effect transistors. Appl Phys Lett. 2011;98:043502.10.1063/1.3546169

- Masahara M, Liu Y, Sakamoto K, et al. Demonstration, analysis, and device design considerations for independent DG MOSFETs. IEEE Trans Electron Devices. 2005;52:2046–2053.10.1109/TED.2005.855063

- Ernst T, Cristoloveanu S, Ghibaudo G, et al. Ultimately thin double-gate SOI MOSFETs. IEEE Trans Electron Devices. 2003;50:830–838.10.1109/TED.2003.811371

- Toumazou C, Shepherd LM, Reed SC, et al. Simultaneous DNA amplification and detection using a pH-sensing semiconductor system. Nat Methods. 2013;10:641–646.10.1038/nmeth.2520

- Sohn I-Y, Kim D-J, Jung J-H, et al. pH sensing characteristics and biosensing application of solution-gated reduced graphene oxide field-effect transistors. Biosens Bioelectron. 2013;45:70–76.10.1016/j.bios.2013.01.051